#### Digital Logic Systems

Recitation 12: Synchronous Circuits: Finite State Machines, Analysis and Synthesis. ISA of DLX

Guy Even Moti Medina

School of Electrical Engineering Tel-Aviv Univ.

June 3, 2019

#### Finite State Machines

#### Definition

A finite state machine (FSM) is a 6-tuple  $\mathcal{A} = \langle Q, \Sigma, \Delta, \delta, \lambda, q_0 \rangle$ , where

- Q is a set of states.

- ullet  $\Sigma$  is the alphabet of the input.

- ullet  $\Delta$  is the alphabet of the output.

- $\delta: Q \times \Sigma \to Q$  is a transition function.

- $\lambda: Q \times \Sigma \to \Delta$  is an output function.

- $q_0 \in Q$  is an initial state.

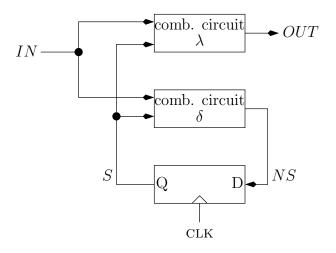

#### The Canonic Form of a Synchronous Circuit

Figure: A synchronous circuit in canonic form.

#### Synthesis and Analysis

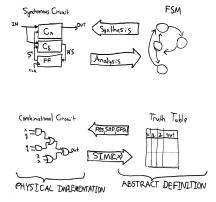

Two tasks are often associated with synchronous circuits:

- **Analysis**: given a synchronous circuit *S*, describe its functionality by an FSM.

- **2 Synthesis**: given an FSM  $\mathcal{A}$ , design a synchronous circuit S that implements  $\mathcal{A}$ .

### Synthesis and Analysis

Two tasks are often associated with synchronous circuits:

- Analysis: given a synchronous circuit *S*, describe its functionality by an FSM.

- **2 Synthesis**: given an FSM  $\mathcal{A}$ , design a synchronous circuit S that implements  $\mathcal{A}$ .

This is somewhat similar to what we already did:

#### **Analysis**

The task of analyzing a synchronous circuit S is carried out as follows.

- **1** Define the FSM  $\mathcal{A} = \langle Q, \Sigma, \Delta, \delta, \lambda, q_0 \rangle$  as follows.

- **1** The set of states is  $Q \stackrel{\triangle}{=} \{0,1\}^k$ , where k denotes the number of flip-flops in S.

- **②** Define the initial state  $q_0$  to be the initial outputs of the flip-flops.

- **3**  $\Sigma = \{0,1\}^{\ell}$ , where  $\ell$  denotes the number of input gates in S.

- **a**  $\Delta = \{0,1\}^r$ , where r denotes the number of output gates in  $S_{\tilde{r}}$

- **Transform** S to a functionally equivalent synchronous circuit  $\tilde{S}$  in canonic form. Compute the truth tables of the combinational circuits  $\lambda$  and  $\delta$ . Define the Boolean functions according to these truth tables.

### Synthesis

Given an FSM  $\mathcal{A} = \langle Q, \Sigma, \Delta, \delta, \lambda, q_0 \rangle$ , the task of designing a synchronous circuit S that implements  $\mathcal{A}$  is carried out as follows.

**1** Encode  $Q, \Sigma$  and  $\Delta$  by binary strings. Formally, let f, g, h denote one-to-one functions, where

$$\begin{split} f: Q &\to \left\{0,1\right\}^k \\ g: \Sigma &\to \left\{0,1\right\}^\ell \\ h: \Delta &\to \left\{0,1\right\}^r. \end{split}$$

② Design a combinational circuit  $C_{\delta}$  that implements the (partial) Boolean function  $B_{\delta}: \{0,1\}^k \times \{0,1\}^\ell \to \{0,1\}^k$  defined by

$$B_{\delta}(f(x), g(y)) \stackrel{\triangle}{=} f(\delta(x, y)), \text{ for every } (x, y) \in Q \times \Sigma.$$

## Synthesis (cont.)

**3** Design a combinational circuit  $C_{\lambda}$  that implements the (partial) Boolean function  $B_{\lambda}: \{0,1\}^k \times \{0,1\}^\ell \to \{0,1\}^r$  defined by

$$B_{\lambda}(f(x),g(z)) \stackrel{\triangle}{=} f(\lambda(x,z)), \text{ for every } (x,z) \in Q \times \Sigma.$$

**4** Let S denote the synchronous circuit in canonic form constructed from k flip-flops and the combinational circuits  $C_{\delta}$  for the next state and  $C_{\lambda}$  for the output.

#### Synthesis - how to encode the states?

Let S denote the synchronous circuit in canonic form constructed from k flip-flops and the combinational circuits  $C_{\delta}$  for the next state and  $C_{\lambda}$  for the output.

The description of the encoding step leaves a great deal of freedom. Since  $|\{0,1\}^k| \geq |Q|$ , it follows that  $k \geq \log_2 |Q|$ , and similar bounds apply to  $\ell$  and r. However, it is not clear that using the smallest lengths is the best idea. Certain encodings lead to more complicated Boolean functions  $B_\delta$  and  $B_\lambda$ . Thus, the question of selecting a "good" encoding is a very complicated task, and there is no simple solution to this problem.

#### **Analysis Question**

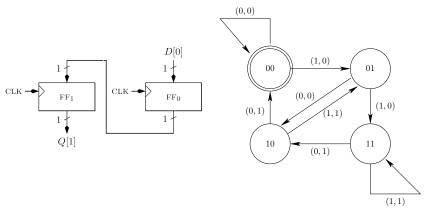

#### Analyze the circuit shift-register(2)

i.e. draw a state diagram of the corresponding FSM.

(a) Shift-Reg(2)

(b) FSM(Shift-Reg(2)) Which is an important graph called De Bruijn Graph  $_{\rm g}$

#### Synthesis Question

#### Design a synchronous circuit S that satisfies the following:

Input:  $x(t), y(t) \in \{0,1\}$ , for every clock cycle t.

Output:  $EQ(t), LT(t), GT(t) \in \{0,1\}$ , for every clock cycle t.

Functionality: Let  $X_t \stackrel{\triangle}{=} \langle x(t), ..., x(0) \rangle$ ,  $Y_t \stackrel{\triangle}{=} \langle y(t), ..., y(0) \rangle$

For every clock cycle  $t \ge 0$ :

$$EQ(t) = \begin{cases} 1, & \text{if } X_t = Y_t, \\ 0, & \text{otherwise}. \end{cases}$$

$$LT(t) = \begin{cases} 1, & \text{if } X_t < Y_t, \\ 0, & \text{otherwise}. \end{cases}$$

$$GT(t) = \begin{cases} 1, & \text{if } X_t < Y_t, \\ 0, & \text{otherwise}. \end{cases}$$

$$GT(t) = \begin{cases} 1, & \text{if } X_t > Y_t, \\ 0, & \text{otherwise}. \end{cases}$$

$$GT(t) = \begin{cases} 1, & \text{if } X_t > Y_t, \\ 0, & \text{otherwise.} \end{cases}$$

- FSM(S) Define the finite state machine  $FSM(S) = \langle Q, \Sigma, \Delta, \delta, \lambda, q_0 \rangle$  that satisfies the specification.

- **2** Synthesize S Implement S by synthesizing FSM(S).

| 5  | 4  | 3  | 2 | 1 | 0 | t                                                         |                |

|----|----|----|---|---|---|-----------------------------------------------------------|----------------|

| 0  | 0  | 1  | 1 | 1 | 0 | x(t)                                                      | 1              |

| 0  | 1  | 1  | 0 | 1 | 0 | y(t)                                                      | Inputs         |

| 14 | 14 | 14 | 6 | 2 | 0 | $X_t \stackrel{\triangle}{=} \langle x(t),, x(0) \rangle$ | 1              |

| 26 | 26 | 10 | 2 | 2 | 0 | $Y_t \stackrel{\triangle}{=} \langle y(t),, y(0) \rangle$ | Interpretation |

| 0  | 0  | 0  | 0 | 1 | 1 | EQ(t)                                                     |                |

| 1  | 1  | 0  | 0 | 0 | 0 | LT(t)                                                     | Outputs        |

| 0  | 0  | 1  | 1 | 0 | 0 | GT(t)                                                     |                |

$\bullet$  Observation 1: The inputs are streamed from the LSB  $\Rightarrow MSB$

| 5  | 4  | 3  | 2 | 1 | 0 | t                                                         |                |

|----|----|----|---|---|---|-----------------------------------------------------------|----------------|

| 0  | 0  | 1  | 1 | 1 | 0 | x(t)                                                      | Land           |

| 0  | 1  | 1  | 0 | 1 | 0 | y(t)                                                      | Inputs         |

| 14 | 14 | 14 | 6 | 2 | 0 | $X_t \stackrel{\triangle}{=} \langle x(t),, x(0) \rangle$ | 1              |

| 26 | 26 | 10 | 2 | 2 | 0 | $Y_t \stackrel{\triangle}{=} \langle y(t),, y(0) \rangle$ | Interpretation |

| 0  | 0  | 0  | 0 | 1 | 1 | EQ(t)                                                     |                |

| 1  | 1  | 0  | 0 | 0 | 0 | LT(t)                                                     | Outputs        |

| 0  | 0  | 1  | 1 | 0 | 0 | GT(t)                                                     |                |

- Observation 1: The inputs are streamed from the LSB  $\Rightarrow$ MSB

- ullet Observation 2: Outputs at time t depend on inputs at time t.

| 5  | 4  | 3  | 2 | 1 | 0 | t                                                         |                |

|----|----|----|---|---|---|-----------------------------------------------------------|----------------|

| 0  | 0  | 1  | 1 | 1 | 0 | x(t)                                                      | la a la        |

| 0  | 1  | 1  | 0 | 1 | 0 | y(t)                                                      | Inputs         |

| 14 | 14 | 14 | 6 | 2 | 0 | $X_t \stackrel{\triangle}{=} \langle x(t),, x(0) \rangle$ | 1              |

| 26 | 26 | 10 | 2 | 2 | 0 | $Y_t \stackrel{\triangle}{=} \langle y(t),, y(0) \rangle$ | Interpretation |

| 0  | 0  | 0  | 0 | 1 | 1 | EQ(t)                                                     |                |

| 1  | 1  | 0  | 0 | 0 | 0 | LT(t)                                                     | Outputs        |

| 0  | 0  | 1  | 1 | 0 | 0 | GT(t)                                                     |                |

- Observation 1: The inputs are streamed from the LSB ⇒MSB

- Observation 2: Outputs at time *t* depend on inputs at time *t*.

- What will our circuit need to "memorize" to be able to determine the output at time *t*?

| 5  | 4  | 3  | 2 | 1 | 0 | t                                                         |                |

|----|----|----|---|---|---|-----------------------------------------------------------|----------------|

| 0  | 0  | 1  | 1 | 1 | 0 | x(t)                                                      |                |

| 0  | 1  | 1  | 0 | 1 | 0 | y(t)                                                      | Inputs         |

| 14 | 14 | 14 | 6 | 2 | 0 | $X_t \stackrel{\triangle}{=} \langle x(t),, x(0) \rangle$ |                |

| 26 | 26 | 10 | 2 | 2 | 0 | $Y_t \stackrel{\triangle}{=} \langle y(t),, y(0) \rangle$ | Interpretation |

| 0  | 0  | 0  | 0 | 1 | 1 | EQ(t)                                                     |                |

| 1  | 1  | 0  | 0 | 0 | 0 | LT(t)                                                     | Outputs        |

| 0  | 0  | 1  | 1 | 0 | 0 | GT(t)                                                     |                |

- Observation 1: The inputs are streamed from the LSB ⇒MSB

- Observation 2: Outputs at time t depend on inputs at time t.

- What will our circuit need to "memorize" to be able to determine the output at time t?

- All the input bits from time 0? Namely  $\{x(\tau), y(\tau)\}_{\tau=0}^{t-1}$

| 5  | 4  | 3  | 2 | 1 | 0 | t                                                         |                |

|----|----|----|---|---|---|-----------------------------------------------------------|----------------|

| 0  | 0  | 1  | 1 | 1 | 0 | x(t)                                                      | lmmuta         |

| 0  | 1  | 1  | 0 | 1 | 0 | y(t)                                                      | Inputs         |

| 14 | 14 | 14 | 6 | 2 | 0 | $X_t \stackrel{\triangle}{=} \langle x(t),, x(0) \rangle$ | 1              |

| 26 | 26 | 10 | 2 | 2 | 0 | $Y_t \stackrel{\triangle}{=} \langle y(t),, y(0) \rangle$ | Interpretation |

| 0  | 0  | 0  | 0 | 1 | 1 | EQ(t)                                                     |                |

| 1  | 1  | 0  | 0 | 0 | 0 | LT(t)                                                     | Outputs        |

| 0  | 0  | 1  | 1 | 0 | 0 | GT(t)                                                     |                |

- Observation 1: The inputs are streamed from the LSB ⇒MSB

- Observation 2: Outputs at time t depend on inputs at time t.

- What will our circuit need to "memorize" to be able to determine the output at time t?

- All the input bits from time 0? Namely  $\{x(\tau), y(\tau)\}_{\tau=0}^{t-1}$ Bad, the required information grows with time

| 5  | 4  | 3  | 2 | 1 | 0 | t                                                         |                |  |  |

|----|----|----|---|---|---|-----------------------------------------------------------|----------------|--|--|

| 0  | 0  | 1  | 1 | 1 | 0 | x(t)                                                      | 1              |  |  |

| 0  | 1  | 1  | 0 | 1 | 0 | y(t)                                                      | Inputs         |  |  |

| 14 | 14 | 14 | 6 | 2 | 0 | $X_t \stackrel{\triangle}{=} \langle x(t),, x(0) \rangle$ | 1              |  |  |

| 26 | 26 | 10 | 2 | 2 | 0 | $Y_t \stackrel{\triangle}{=} \langle y(t),, y(0) \rangle$ | Interpretation |  |  |

| 0  | 0  | 0  | 0 | 1 | 1 | EQ(t)                                                     |                |  |  |

| 1  | 1  | 0  | 0 | 0 | 0 | LT(t)                                                     | Outputs        |  |  |

| 0  | 0  | 1  | 1 | 0 | 0 | GT(t)                                                     |                |  |  |

- Observation 1: The inputs are streamed from the LSB ⇒MSB

- Observation 2: Outputs at time t depend on inputs at time t.

- What will our circuit need to "memorize" to be able to determine the output at time t?

- All the input bits from time 0? Namely  $\{x(\tau), y(\tau)\}_{\tau=0}^{t-1}$  Bad, the required information grows with time

- Just the relation between  $X_{t-1}$  and  $Y_{t-1}$ .

| 5  | 4  | 3  | 2 | 1 | 0 | t                                                         |                |

|----|----|----|---|---|---|-----------------------------------------------------------|----------------|

| 0  | 0  | 1  | 1 | 1 | 0 | x(t)                                                      |                |

| 0  | 1  | 1  | 0 | 1 | 0 | y(t)                                                      | Inputs         |

| 14 | 14 | 14 | 6 | 2 | 0 | $X_t \stackrel{\triangle}{=} \langle x(t),, x(0) \rangle$ |                |

| 26 | 26 | 10 | 2 | 2 | 0 | $Y_t \stackrel{\triangle}{=} \langle y(t),, y(0) \rangle$ | Interpretation |

| 0  | 0  | 0  | 0 | 1 | 1 | EQ(t)                                                     |                |

| 1  | 1  | 0  | 0 | 0 | 0 | LT(t)                                                     | Outputs        |

| 0  | 0  | 1  | 1 | 0 | 0 | GT(t)                                                     | -              |

- Observation 1: The inputs are streamed from the LSB ⇒MSB

- Observation 2: Outputs at time t depend on inputs at time t.

- What will our circuit need to "memorize" to be able to determine the output at time t?

- All the input bits from time 0? Namely  $\{x(\tau), y(\tau)\}_{\tau=0}^{t-1}$  Bad, the required information grows with time

- Just the relation between  $X_{t-1}$  and  $Y_{t-1}$ . Good, only 3 options "equal" "less than" "greater than"

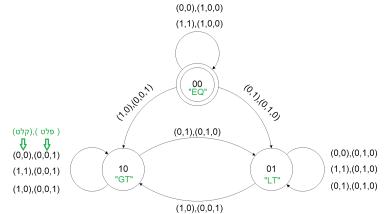

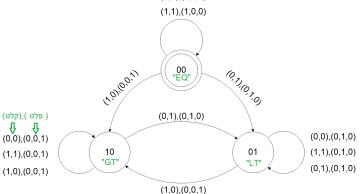

#### FSM - Declare the states and the encodings

- Let's Describe the  $FSM(S) = \langle Q, \Sigma, \Delta, \delta, \lambda, q_0 \rangle$  and also provide the encodings:

- $Q \triangleq \{0,1\}^2$  the states 00 for  $X_t = Y_t$  (The "EQ" state) 01 for  $X_t < Y_t$  (The "LT" state) 10 for  $X_t > Y_t$  (The "GT" state)

- $\Sigma \triangleq \{0,1\}^2$  the input alphabet. The two inputs x(t), y(t) are simply concatenated together.

- $\Delta \stackrel{\triangle}{=} \{0,1\}^3$  the output alphabet 100 for EQ(t) 010 for LT(t) 001 for GT(t)

- $q_0$  is 00, (The equality state)

#### FSM - State Diagram

- Let's Describe the  $FSM(S) = \langle Q, \Sigma, \Delta, \frac{\delta}{\delta}, \lambda, q_0 \rangle$

- $\bullet$   $\delta$  state-transfer function, receives the current input and the current state and returns the next state.

- $\lambda$  output-function, receives the current input and the current state and returns the current output.

- We describe the two functions using a state diagram:

# Synthesis - Recovering truth table of $\delta$ and $\lambda$ from FSM

Translate each state into 4 rows of the table. Note that S[1:0] = 11 is an inaccessible state.

| Current State                     | S[1] | S[0] | Х | у | NS[1] | NS[0] | EQ | LT | GT   |

|-----------------------------------|------|------|---|---|-------|-------|----|----|------|

| (Ø,0),(1,0,0)                     | 0    | 0    | 0 | 0 | 0     | 0     | 1  | 0  | 0    |

| (1,1),(1,0,0)                     | 0    | 0    | 0 | 1 | 0     | 1     | 0  | 1  | 0    |

| 00,1,00                           | 0    | 0    | 1 | 0 | 1     | 0     | 0  | 0  | 1    |

| 1.0 GT (0,7,0)                    | 0    | 0    | 1 | 1 | 0     | 0     | 1  | 0  | 0    |

|                                   | 0    | 1    | 0 | 0 | 0     | 1     | 0  | 1  | 0    |

| (0,0),(0,1,0)<br>(1,1),(0,1,0)    | 0    | 1    | 0 | 1 | 0     | 1     | 0  | 1  | 0    |

| to GT (0,1),(0,1,0)               | 0    | 1    | 1 | 0 | 1     | 0     | 0  | 0  | 1    |

| (1,0),(0,0,1)                     | 0    | 1    | 1 | 1 | 0     | 1     | 0  | 1  | 0    |

| ( פלט ),(קלט)                     | 1    | 0    | 0 | 0 | 1     | 0     | 0  | 0  | 1    |

| (0,0),(0,0,1) to LT (0,1),(0,1,0) | 1    | 0    | 0 | 1 | 0     | 1     | 0  | 1  | 0    |

| (1,1),(0,0,1) ( 10 "GT"           | 1    | 0    | 1 | 0 | 1     | 0     | 0  | 0  | 1    |

| (1,0),(0,0,1)                     | 1    | 0    | 1 | 1 | 1     | 0     | 0  | 0  | 1    |

|                                   |      |      |   |   | I     |       |    |    | 14/: |

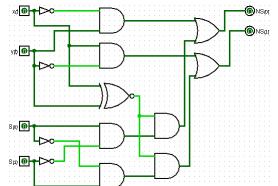

## Synthesis - Implementing $C_{\delta}$ (skipping truth table)

- The  $C_{\delta}$  state-transfer circuit receives the  $IN = x(t) \circ y(t)$ and the current state S and outputs the next state NS.

- We can derive the  $C_{\delta}$  formulas directly from the FSM(S):

$$NS = 00 \Leftrightarrow S = 00 \text{ and } x(t) = y(t)$$

$NS = 01 \Leftrightarrow x(t) < y(t) \text{ or } (S = 01 \text{ and } x(t) = y(t))$

$NS = 10 \Leftrightarrow x(t) > y(t) \text{ or } (S = 10 \text{ and } x(t) = y(t))$

$$(0,0),(1,0,0)$$

$$(1,1),(1,0,0)$$

$$(0,0),(0,0,1)$$

$$(1,1),(0,0,1)$$

$$(1,1),(0,0,1)$$

$$(1,1),(0,0,1)$$

$$(1,1),(0,0,1)$$

$$(1,1),(0,0,1)$$

$$(1,1),(0,0,1)$$

$$(1,1),(0,0,1)$$

$$(1,1),(0,1,0)$$

$$(0,1),(0,1,0)$$

$$(0,1),(0,1,0)$$

(1,0),(0,0,1)

(1,0),(0,0,1)

## Synthesis - Implementing $C_{\delta}$

• We can derive the  $C_{\delta}$  formulas from the FSM(S):

$$NS = 00 \Leftrightarrow S = 00 \text{ and } x(t) = y(t)$$

$NS = 01 \Leftrightarrow x(t) < y(t) \text{ or } (S = 01 \text{ and } x(t) = y(t))$

$NS = 10 \Leftrightarrow x(t) > y(t) \text{ or } (S = 10 \text{ and } x(t) = y(t))$

• We further provide the boolean function per each flip-flop:  $NS[0] = \bar{x} \cdot y + (\overline{S[1]} \cdot S[0] \cdot NXOR(x, y))$

$$NS[1] = x \cdot \overline{y} + (S[1] \cdot \overline{S[0]} \cdot NXOR(x, y))$$

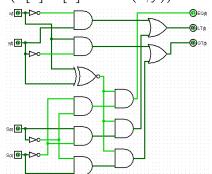

## Synthesis - Implementing $C_{\lambda}$ (skipping truth table)

- The  $C_{\lambda}$  output circuit receives the  $IN = x(t) \circ y(t)$  and the current state S and generates outputs EQ(t),LT(t),GT(t).

- We can derive the  $C_{\lambda}$  formulas directly from the FSM(S):

We can derive the

$$C_{\lambda}$$

formulas directly from the FSM(S)  $EQ = 1 \Leftrightarrow S = 00$  and  $x(t) = y(t)$   $LT = 1 \Leftrightarrow x(t) < y(t)$  or  $(S = 01 \text{ and } x(t) = y(t))$   $GT = 1 \Leftrightarrow x(t) > y(t)$  or  $(S = 10 \text{ and } x(t) = y(t))$   $(0,0),(1,0,0)$

## Synthesis - Implementing $C_{\lambda}$

• We can derive the  $C_{\lambda}$  formulas from the FSM(S):

$$EQ = 1 \Leftrightarrow S = 00 \text{ and } x(t) = y(t)$$

$LT = 1 \Leftrightarrow x(t) < y(t) \text{ or } (S = 01 \text{ and } x(t) = y(t))$

$GT = 1 \Leftrightarrow x(t) > y(t) \text{ or } (S = 10 \text{ and } x(t) = y(t))$

• We further provide the boolean function per each flip-flop:  $EQ = \overline{S[0]} \cdot \overline{S[1]} \cdot NXOR(x, y)$

$$LT = \bar{x} \cdot y + (\overline{S[1]} \cdot \underline{S[0]} \cdot NXOR(x, y))$$

$$GT = x \cdot \bar{y} + (S[1] \cdot \overline{S[0]} \cdot NXOR(x, y))$$

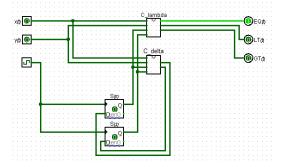

#### Synthesis - Putting it all together into *S*

- Instantiate the  $C_{\delta}$  and the  $C_{\lambda}$  circuits.

- Add *k* flip-flops for the state storage.

#### **RESAb3** simulator

RESAb3 software contains the **text editor** for writing the assembly code, and the **DLX simulator** for running it.

- Open the Resa program and choose a text editor.

- Write a program in a text editor, and compile it to ensure that it has no compilation errors. This should generate the ".cod" file with the machine code.

- § File→New to open simulator window.

- In the simulator window File→Open COD to load the machine code.

- Simulator→Add Watch to observe a particular memory cell.

- Run→Run Until Halt to execute the whole program